Transforming Chip Energy Efficiency to Meet Escalating AI Requirements

The rapid expansion of artificial intelligence applications has dramatically increased the demand for computational resources, leading to a critical shortage in data center capacity worldwide. Large language models, which underpin many modern AI systems, consume enormous amounts of power during both their training and inference stages. This surge in energy consumption has placed energy efficiency at the forefront for semiconductor manufacturers aiming to boost performance while minimizing power usage.

Breakthrough Power Delivery Innovations from Emerging Semiconductor Firms

A notable newcomer addressing this challenge is PowerLattice, a startup founded by industry veterans with experience at Qualcomm, NUVIA, and Intel. Established in 2023, PowerLattice has developed an innovative chiplet-based technology that reportedly cuts power consumption by more then half-a significant advancement toward reducing processor energy waste.

This innovation involves embedding compact power delivery chiplets directly next to processing units on the silicon die. By positioning these power sources closer to where electricity is consumed within the chip itself, transmission losses typically caused by longer internal pathways are drastically minimized.

industry Support and Initial Production Successes

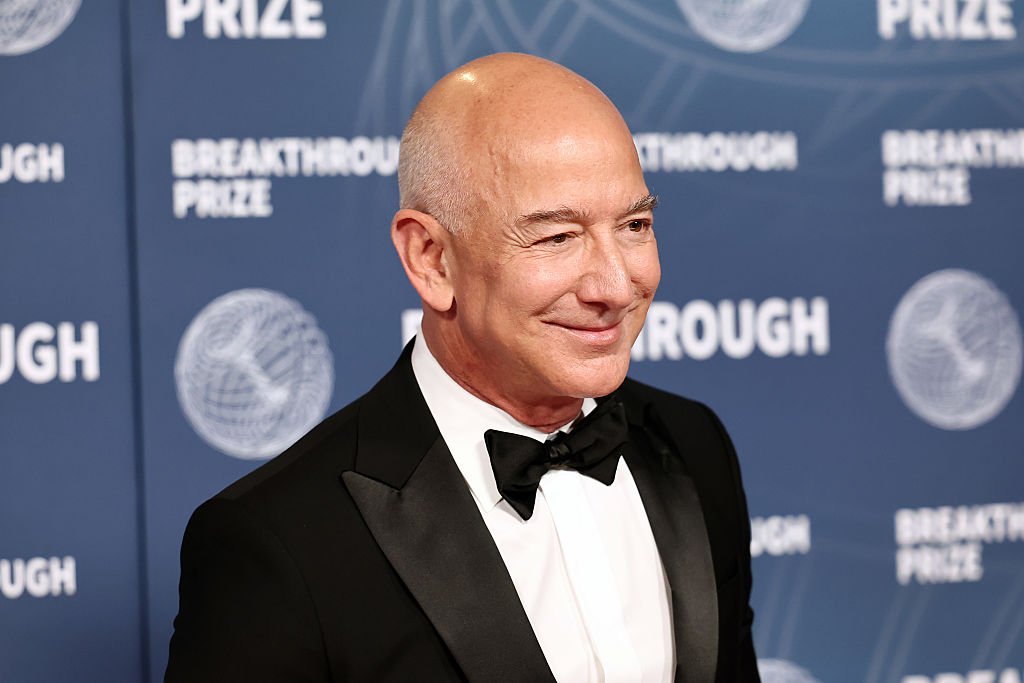

The company’s approach has received strong backing from Pat Gelsinger-former CEO of Intel and current general partner at Playground Global-who highlights their work as addressing one of semiconductor design’s toughest challenges: efficient on-chip power management. His endorsement adds substantial credibility given his deep expertise in this field.

PowerLattice recently reached a key milestone with mass production of its first batch of chiplets thru TSMC’s fabrication facilities. These components are now undergoing extensive validation testing alongside an undisclosed manufacturing partner focused on confirming real-world performance improvements.

collaborations with Leading Chipmakers and AI Innovators

The startup intends to broaden access to its technology for evaluation starting early 2026.Potential collaborators include major players such as Nvidia, Broadcom, AMD as well as specialized AI hardware firms like Cerberus and Grok. Additionally,startups supported by playground Global-including d-Matrix and NextSilicon-are slated for trials.

This varied group reflects widespread interest across customary semiconductor companies and emerging AI-focused hardware developers eager to enhance energy efficiency without compromising computational throughput or speed.

A Competitive Arena Centered on Energy Reduction

PowerLattice operates amid several competitors pursuing similar objectives; notably Empower Semiconductor recently raised over $140 million in Series D funding aimed at advancing low-power chip technologies. Despite this competition, Gelsinger emphasizes that achieving more than 50% reduction in power consumption represents a remarkable feat unlikely matched easily by rivals.

“The concept is bold with significant advantages,” he states,“and we expect others will pursue comparable innovations once our results become public.”

The Urgent Need for Sustainable Semiconductor Solutions

The global data center industry currently accounts for roughly 1% of total electricity use worldwide-a figure projected to climb sharply due to double-digit annual growth rates in AI workloads through 2030.Innovations like those pioneered by PowerLattice could be instrumental not only in reducing environmental footprints but also enabling advanced computing capabilities essential across diverse fields such as autonomous transportation systems, natural language processing breakthroughs, personalized medicine simulations, and beyond.

- Example: Autonomous drone fleets require continuous real-time data processing under strict latency limits; lowering onboard processor energy demands extends operational time significantly without sacrificing mission-critical computations or safety protocols.

- Example: In precision agriculture analytics involving satellite imagery combined with machine learning models-energy-efficient chips accelerate insights while cutting costs across farming operations globally.

Aiming Toward Scalable Manufacturing Investment

The promising initial outcomes position PowerLattice advantageously ahead of anticipated larger funding rounds designed specifically for scaling global manufacturing efforts-a vital step toward mainstream adoption within markets dominated by giants like intel and Nvidia but increasingly shaped by agile startups driving sustainability-focused innovation deeply embedded within silicon architecture design philosophies.

Navigating the Future: Harmonizing Performance With Environmental Obligation in Chip Engineering

Tackling inefficiencies inherent within current processor designs remains one crucial frontier where meaningful progress can foster greener computing ecosystems supporting exponential growth trajectories seen throughout artificial intelligence sectors today-and tomorrow’s innovations depend heavily on foundational advancements underway at companies like PowerLattice.

as demand intensifies relentlessly across industries reliant upon sophisticated machine learning-from financial risk analysis platforms handling petabytes daily up through climate modeling engines requiring massive parallelism-the race is no longer just about raw compute capacity but smarter computation delivered sustainably.

Ultimately,energy efficiency wil be a defining competitive edge alongside raw speed or memory bandwidth when assessing next-generation semiconductors powering our digital future.